# Electrical properties of MOS capacitors formed by PEALD grown Al<sub>2</sub>O<sub>3</sub> on silicon

© A.M. Mahajan\*<sup>¶</sup>, A.G. Khairnar\*<sup>¶¶</sup>, B.J. Thibeault<sup>†</sup>

\* Department of Electronics, North Maharashtra University, 425001 Maharashtra, India

<sup>†</sup> ECE Department, University of California Santa Barbara, CA, USA

(Получена 23 мая 2013 г. Принята к печати 17 июля 2013 г.)

In the present work, we have grown 2.83 nm thin Al<sub>2</sub>O<sub>3</sub> films directly on pre-cleaned *p*-Si(100) substrate using precursor Trimethyl Aluminium (TMA) with substrate temperature of 300°C in a Plasma Enhanced Atomic Layer Deposition (PEALD) chamber. The MOS capacitors were fabricated by depositing Pt/Ti metal bilayer through shadow mask on Al<sub>2</sub>O<sub>3</sub> high-k by electron beam evaporation system. The MOS devices were characterized to evaluate the electrical properties using a capacitance voltage (*CV*) set-up. The dielectric constant calculated through the *CV* analysis is 8.32 for Al<sub>2</sub>O<sub>3</sub> resulting in the equivalent oxide thickness (EOT) of 1.33 nm. The flat-band shift of 0.3 V is observed in the *CV* curve. This slight positive shift in flat-band voltage is due to the presence of some negative trap charges in Pt/Ti/ALD-Al<sub>2</sub>O<sub>3</sub>/p-Si MOS capacitor. The low leakage current density of  $3.08 \cdot 10^{-10}$  A/cm<sup>2</sup> is observed in the *JV* curve at 1 V. The Si/Al<sub>2</sub>O<sub>3</sub> barrier height  $\Phi_B$  and the value of  $J_{\text{FN}}$  are calculated to be 2.78 eV and  $3.4 \cdot 10^{-5}$  A/cm<sup>2</sup> respectively.

### 1. INTRODUCTION

The Metal-Oxide-Semiconductor Field Effect Transistors (MOSFETs) are the basic building blocks of the current ULSI circuits. The processing speed and electrical power dissipation which are dependent on the geometrical size of MOSFET decides performance of silicon ULSI devices. The miniaturization of the metal oxide semiconductor (MOS) devices following the Moore's law has lead to the extreme thinning of the commonly used SiO<sub>2</sub> gate oxide. However, this thinning has reached its limits because of the dramatic increase of the leakage current through the oxide, causing the degradation of the devices [1-4]. In order to find appropriate substitute for insulating SiO<sub>2</sub> the traditional gate oxide in silicon based nanoelectronics MOS devices need the higher-k dielectrics to minimize the EOT (Equivalent Oxide Thickness) for better performance. A variety of high-permittivity metal oxides have been intensely studied during the last decade such as HfO<sub>2</sub>, TiO<sub>2</sub>, CeO<sub>2</sub>, ZrO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, LaAlO<sub>3</sub>, HfSiO etc [5-6]. Among the properties of high-k oxides, the thermal stability of high-k dielectric on silicon is an important issue for future MOSFET devices. Al<sub>2</sub>O<sub>3</sub> exhibits large band gap  $7-8 \,\mathrm{eV}$  high field strength, excellent thermodynamic stability on Si to reduce the tunneling current for the same gate capacitance, dielectric constant of 9 and large band offsets [7–9]. The deposition methods and the deposition conditions tend to determine the crystallinity and purity of deposited dielectric thin films. High temperature annealing can result in the crystallization and densification of dielectric materials. Deposition of high-k layer on Si substrate can be done by variety of techniques such as ALD [10], RF Sputtering [11], MOCVD [12], PLD [13], sol-gel [14,15],

PEALD [16] etc. In nanoelectronics, continuous shrinking of devices improves the performance, which sets challenging requirements for the integrated circuit (IC) fabrication. As requirements tighten, the novel thin film deposition techniques are needed in many applications. The current interest in ALD in the nanoelectronics industry stems from the unique characteristics that, this method offers deposition of ultrathin films on a large substrate area with excellent properties and with control of thickness and composition at sub-nanometer level [10]. As the nanoelectronics industry looks to transition to both three dimensional transistor and interconnect technologies at the < 22 nm node, highly conformal dielectric coatings with precise thickness control are increasingly being demanded. Plasma enhanced atomic layer deposition (PEALD) currently plays this role for most of the applications requiring low temperature processing, good step coverage and precise thickness requirements. In PEALD, gases that provide radical atoms or ions for the reaction under the plasma condition are normally inactive with the metal precursors at the process temperature. Thus no deposition can be expected where plasma doesn't exist. The properties of dielectric thin films can be studied by fabricating metal oxide semiconductor structure by depositing suitable metal gates. Candidates for new metallic gates have many requirements which include appropriate work function good thermal and chemical interface stability with underlying dielectric and high carrier concentration and process compatibility with current and future CMOS devices. Metal bi-layered electrode structures of ultrathin layer of low work function metal followed by comparatively thicker layer of high work function metal, like Nb/W, Ti/Pt, Ti/W, Al/TaN etc have been used in recent past for the purpose of forming the better MOS devices through the work function tuning [17]. This work reports the deposition of Al<sub>2</sub>O<sub>3</sub> high-k thin film on silicon substrate and fabrication

<sup>¶</sup> E-mail: ammahajan@nmu.ac.in

<sup>¶¶</sup> E-mail: agkhairnar@gmail.com

of MOS capacitors using Pt/Ti bi-layer metal electrodes. The experimental details are described in the second section of the paper and the third section describes some related theoretical aspects. Results are described in fourth section and fifth section concludes the paper.

## 2. EXPERIMENTAL

P-type Si(100) substrates were used for the deposition of Al<sub>2</sub>O<sub>3</sub> high-k thin films. Substrates were ultrasonically cleaned in Acetone for 2 min at 15°C and methanol for 1 min at 15°C followed by a rinse in deionized (DI) water for organic removal. Samples were then cleaned in buffered Hydrofluoric acid (BHF) for native oxide removal followed by a rinse in DI water. The substrates were then dried and put into the deposition chamber of the PEALD (Model-Oxford FlexAL) system. Trimethyl Aluminium (TMA) and oxygen plasma were used as the precursor materials for the Al<sub>2</sub>O<sub>3</sub> deposition at 300°C substrate temperature. The ALD growth cycle consisted of the following steps: 10 ms TMA dose at 20 mT chamber pressure, 2 s of argon purge, 5 s of oxygen plasma at 250 W ICP power and 10 mT chamber pressure. The Pt/Ti metal bilayer electrodes were deposited by electron beam evaporation (CHA model no. SEC-600) through a shadow mask with electrode area of  $1.77 \cdot 10^{-4} \text{ cm}^2$  to fabricate the MOS capacitors. Ti and Pt have thicknesses of 2 nm and 20 nm at the deposition rate 0.2 Å/s and 0.5 Å/s respectively. Rapid thermal annealing (RTA, AET Model No-RX-6) was performed on the fabricated Pt/Ti/ALD-Al<sub>2</sub>O<sub>3</sub>/p-Si MOS capacitors at 350°C in a forming gas environment  $(N_2 : H_2, 90: 10)$  for 30 min. Backside metal contact was formed by depositing the Aluminum using the thermal evaporation system. The deposited films and fabricated MOS capacitor were characterized using a spectroscopic ellipsometer (M2000DI JA Woollam Co-Inc) for film thickness measurement, capacitance-voltage (Agilent 4284A LCR) and current-voltage (semiconductor characterization system 4200) for electrical properties.

### 3. RESULTS AND DISCUSSION

#### 3.1. Ellipsometry

The thickness of the  $Al_2O_3$  film was found to be 2.83 nm measured using variable angle spectroscopic ellipsometry. The equivalent oxide thickness (EOT) of 1.32 nm has been determined by using physical thickness of  $Al_2O_3$  layer and dielectric constant obtained from the capacitance voltage (*CV*) measurement, which is compatible to the current technology nodes.

# 3.2. Capacitance–Voltage (CV) and Conductance Voltage (GV) Measurement

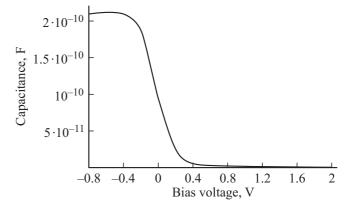

The Pt/Ti/ALD-Al<sub>2</sub>O<sub>3</sub>/*p*-Si MOS capacitor was characterized by the Agilent 4284A LCR meter for the measurements of dielectric properties of the fabricated MOS structure. A typical *CV* characteristics curve of MOS structure is shown in the fig. 1. The dielectric constant (k) value of sample annealed at different temperatures was extracted from the accumulation level of a *CV* curve and was calculated using the following equation

$$k = (C_{\rm ox} t_{\rm ox}) / (\varepsilon_0 A). \tag{1}$$

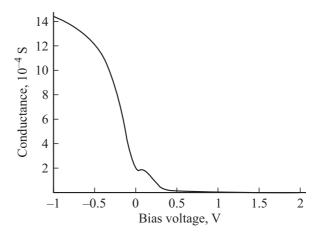

Where,  $C_{\text{ox}}$  is the oxide capacitance,  $t_{\text{ox}}$  is the thickness of oxide layer,  $\varepsilon_0$  is the permittivity of free space and Ais the electrode area. The dielectric constant determined from accumulation capacitance of CV curve obtained at 1 MHz is 8.32. In CV curve a slight negative shift is observed in the flat-band voltage because of the presence of positive trap charges ( $Q_{\text{eff}}$ ) in the Al<sub>2</sub>O<sub>3</sub> MOS capacitor. The  $Q_{\text{eff}}$  can be found by using Eq. (2) and thus calculated to be  $4.88 \cdot 10^{12} \text{ cm}^{-2}$  [18]. The frequency dispersion in CV curves is observed in figure 1 due to the presence of trap charges. The value of interface trap density ( $D_{\text{it}}$ ) is determined from the CV and conductance–voltage (GV) curve of Fig. 1 and 2 and calculated from the Hill–Coleman

**Figure 1.** Capacitance-Voltage characteristics of Pt/Ti/ALD-Al<sub>2</sub>O<sub>3</sub>/*p*-Si MOS capacitor.

**Figure 2.** Conductance-Voltage characteristics of Pt/Ti/ALD–Al<sub>2</sub>O<sub>3</sub>/*p*-Si MOS capacitor.

method using Eq. (3) [19]:

$$Q_{\rm eff} = (\Delta V_{\rm FB} C_{\rm ox})/qA, \qquad (2)$$

$$D_{\rm it} = \frac{2\omega C_{\rm ox}^2 G_{\rm max}}{qA\{G_{\rm max}^2 + \omega^2 [C_{\rm ox} - C_m(G_{\rm max})]^2\}}.$$

(3)

Where,  $\Delta V_{\rm FB}$  is the flat band voltage shift, q is electronic charge,  $C_m$  is maximum capacitance,  $G_{\rm max}$  is the maximum conductance and  $\omega$  is frequency. The value of  $D_{\rm it}$  for 1 MHz frequency is found to be  $1.30 \cdot 10^{13} \,{\rm cm}^{-2} \,{\rm eV}^{-1}$ . The density of interface trap is very high and may be due to poor interface quality at Si/Al<sub>2</sub>O<sub>3</sub> due to direct deposition of Al<sub>2</sub>O<sub>3</sub> on *p*-Si substrate.

#### 3.3. Current density-voltage (JV) measurement

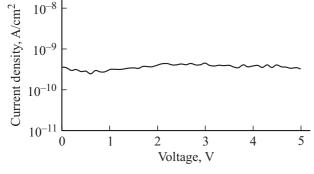

Fig. 3 shows the leakage current density–voltage (JV) curve of 2.83 nm thin Al<sub>2</sub>O<sub>3</sub> based MOS capacitor having a leakage current density of  $3.08 \cdot 10^{-10}$  A/cm<sup>2</sup> of forming gas annealed Al<sub>2</sub>O<sub>3</sub> at 1 V biasing voltage, indicating good electrical integrity at 1 V biasing voltage.

According to quantum mechanics, the charge carriers tunnel through triangular barrier into the conduction band of an oxide; it is termed as FN tunneling [20–24]. The leakage current density found by FN tunneling,  $J_{\rm FN}$ , can be described by

$$J_{\rm FN} = AE^2 \exp(-B/E), \tag{4}$$

where,

$$A = q^3 m_0 / (8\pi h m^* \Phi_B), \qquad (5)$$

$$B = 4(2m^*)^{1/2}(q\Phi_B)^{3/2}/(3qh/2\pi), \tag{6}$$

$$I = I/A \tag{7}$$

$$E = (V_G + V_{\rm FB})/EOT, \tag{8}$$

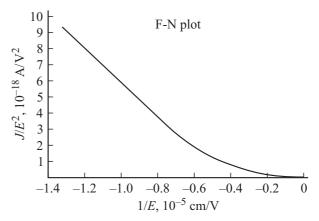

where A is the Richardson constant, q is the electronic charge, h is Planck's constant,  $m_0$  is the free electron mass,  $m^*$  is the effective electron mass in oxide, and  $\Phi_B$  is the barrier height between the p-type Si and gate oxide,  $V_G$  is the gate voltage. Fig. 4 shows a plot of  $J/E^2vs1/E$  resulting from the data in Fig. 3. The tunneling parameter B is the slope of the linear region in the FN plot  $[\ln(J/E^2)vs1/E]$ .

**Figure 3.** Current density vs voltage (JV) curve of Pt/Ti/ALD-Al<sub>2</sub>O<sub>3</sub>/*p*-Si MOS capacitor.

**Figure 4.** Fowler-Nordheim (FN) plot of Pt/Ti/ALD-Al<sub>2</sub>O<sub>3</sub>/*p*-Si MOS capacitor.

The magnitude of this slope can be used to calculate the Si/Al<sub>2</sub>O<sub>3</sub> barrier height. *E* is the oxide electric field derived from the applied potential corrected for the flatband voltage,  $V_{\rm FB} = 0.3$  V, divided by the film equivalent oxide thickness. The effective mass of an electron in Al<sub>2</sub>O<sub>3</sub> is  $m^* = 0.35m_0$ . Using this effective mass, the Si/Al<sub>2</sub>O<sub>3</sub> barrier height  $\Phi_B$  is calculated as 2.78 eV based on the data in Fig. 4 and the value of  $J_{\rm FN}$  is calculated to be  $3.4 \cdot 10^{-5}$  A/cm<sup>2</sup> at 4 MV/cm.

### 4. CONCLUSIONS

The Al<sub>2</sub>O<sub>3</sub> thin films were successfully deposited with controlled thickness using PEALD technique and the Pt/Ti/ALD-Al<sub>2</sub>O<sub>3</sub>/*p*-Si MOS capacitors were fabricated by depositing Ti/Pt bi-layer metal contacts. We have investigated the electric properties like density of interface traps, leakage current density and conduction mechanism which holds good electrical integrity from the CV/IV curves obtained for fabricated MOS capacitors. These values of the electrical characteristics of the fabricated Pt/Ti/ALD-Al<sub>2</sub>O<sub>3</sub>/*p*-Si MOS capacitors can be considered to be suitable for current technology nodes.

Acknowledgement: Authors are thankful to NNIN Nanofab lab UCSB, CA, USA for providing necessary fabrication facilities, CEN IIT Mumbai under INUP program and UGC, New Delhi for providing financial assistance to carry out present work [F. No. 36-181/2008(SR)]. A.G. Khairnar is thankful to CSIR New Delhi, India for providing Senior Research Fellowship for carrying out this work [File No. 09/728(0029)/2012-EMR-I].

#### References

Pi-chun Juan, Chuan-hsi Liu, Cheng-li Lin, Shin-chun Ju, Main-gwo Chen Ingram Yin-ku Chang, and Jong-hong Lu. Jpn. J. Appl. Phys., 48, 05DA02 (2009).

Физика и техника полупроводников, 2014, том 48, вып. 4

- [2] H. Garcial, S. Duefias, H. Castan, A. Gomezl, L. Bailon', K. Kukli, T. Hatanpaa, J. Aarik, A. Aidla, M. Ritala, M. Leskelii. *Proc. of the 2009 Spanish Conf. on Electron Devices* (Febr. 11–13, 2009) c. 223.

- [3] H.Y. Yu, M.F. Li, B. J. Cho, C.C. Yeo, M.S. Joo, D.-L. Kwong, J.S. Pan, C.H. Ang, J.Z. Zheng, S. Ramanathan. Appl. Phys. Lett., 81, 376 (2002).

- [4] M. Liu, G. Hea, L.Q. Zhu a, Q. Fang a,b, G.H. Li a, L.D. Zhang. Appl. Surf. Sci., 252, 6206 (2006).

- [5] Gang He, Zhaoqi Sun, Guang Li, Lide Zhan. Critical Rev. Sol. St. and Mater. Sci., 37, 131 (2012).

- [6] Chun Zhao, C.Z. Zhao, M. Werner, S. Taylor, P.R. Chalker. International Scholarly Research Network ISRN Nanotechnology, 2012, Article ID 689 023, 35 p.

- [7] K.Y. Gao, F. Speck, K. Emtsev, Th. Seyller, L. Ley. J. Appl. Phys., **102**, 094 503 (2007).

- [8] Liu Yan-Ping, Lan-Wei, He Zhi-Wei, Wang Yin-Yue. Chin. Phys. Lett., **23**, 2236 (2006).

- [9] J.-Y. Son, S.-W. Jeong, K.-S. Kim, Yonghan Roh. J. Korean Phys. Soc., 51, S238 (2007).

- [10] J.C. Hackley, J.D. Demaree, T. Gougousi. Mater. Res. Soc. Symp. Proc., 1073, 1073-H04-19 (2008).

- [11] P.M. Tirmali, A.G. Khairnar, B.N. Joshi, A.M. Mahajan. Sol. St. Electron., 62, 44 (2011).

- [12] M. Sato, T. Aoyama, Y. Nara, Y. Ohji. Jpn. J. Appl. Phys. 48, 04C002 (2009).

- [13] J. Lappalainen, H.L. Tuller, V. Lantto. J. Electroceram., 13, 129 (2004).

- [14] M.-G. Blanchin, B. Canut, Y Lambert, V.S. Teodorescu, A. Baraŭ, M. Zaharescu. J. Sol-Gel Sci. Technol., 47, 165 (2008).

- [15] A.G. Khairnar, A.M. Mahajan. Bull. Mater. Sci., 36, 259 (2013).

- [16] Sandy X. Lao, Ryan M. Martin, Jane P. Chang. J. Vac. Sci. Technol. A, 23-3, 488 (2005).

- [17] Metal Ching-Huang Lu, Gloria M.T. Wong, Michael D. Deal, Wilman Tsai, Prashant Majhi, Chi On Chui, Mark R. Visokay, James J. Chambers, Luigi Colombo, Bruce M. Clemens, Yoshio Nish. IEEE Electron. Dev. Lett., 26-7 (2005).

- [18] A.G. Khairnar, A.M. Mahajan. Sol. St. Sci., 15, 24 (2013).

- [19] E.H. Oulachgar, C. Aktik, M. Scarlete, S. Dostie, R. Sowerby, S. Gujrathi. Appl. Phys. Lett., **101**, 084107 (2007).

- [20] H.J. Quah, K.Y. Cheong, Z. Hassan, Z. Lockman. IEEE Trans. Electron. Dev., 58, 122 (2011).

- [21] P. Laha, A.B. Panda, S. Dahiwale, K. Date, K.R. Patil, P.K. Barhai, A.K. Das, I. Banerjee, S.K. Mahapatra. Thin Sol. Films, **519**, 1530 (2010).

- [22] K.Y. Cheong, J.H. Moon, H.J. Kim, W. Bahng, Nam-Kyun Kim. J. Appl. Phys., **103**, 084 113 (2008).

- [23] W.J. Zhu, Tso-Ping Ma, Takashi Tamagawa, J. Kim, Y. Di. IEEE Electron. Dev. Lett., 23, 97 (2002).

- [24] M.D. Groner, J.W. Elam, F.H. Fabreguette, S.M. George. Thin Sol. Films, 413, 186 (2002).

Редактор Т.А. Полянская